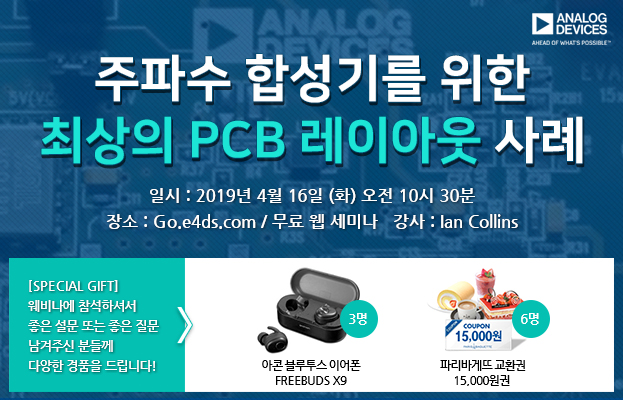

주파수 합성기를 위한 최상의 PCB 레이아웃 사례

2019-04-16 10:30~11:50

ADI / Ian Collins

이번 웨비나에서는 주파수 합성기의 성능을 최적화하기 위한 PCB 설계 guide를 제시합니다.

최상의 PLL의 성능을 유지하고, spurious emission 및 주변 소자간 interference를 최소화하는 기법에 대해 설명할 것입니다.

본 웨비나의 발표자 이안 콜린스는 아나로그 디바이스사의 Microwave Frequency generation group의 application manager로서, PLL 및 VCO제품에 대한 전문가입니다.

웨비나에서 다뤄볼 내용은 다음과 같습니다.

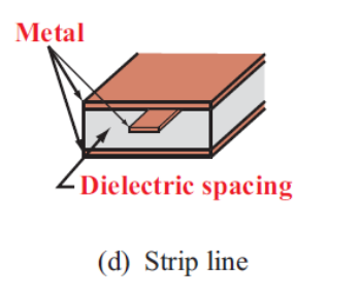

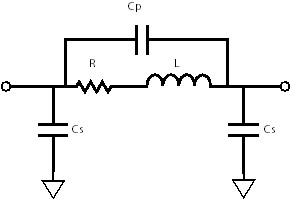

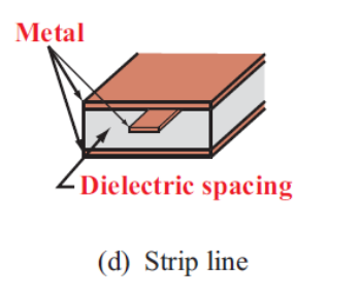

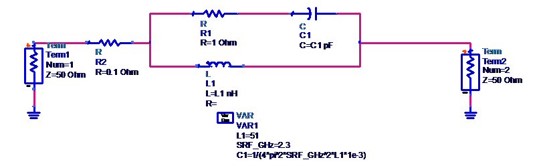

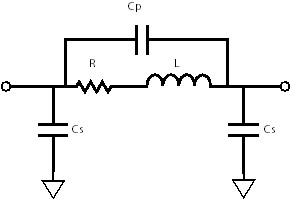

첫째, 이러한 유형의 PCB의 특성상 전송 라인 이론과 사용 가능한 다른 유전체 재료를 검토하는 것이 중요하기 때문에, 수동 부품 선택 및 관련한 모범 사례를 살펴보고, LPF(Low-Pass Filter)와 RF 회로에 적합한 커패시터에 대해 알아볼 것입니다.

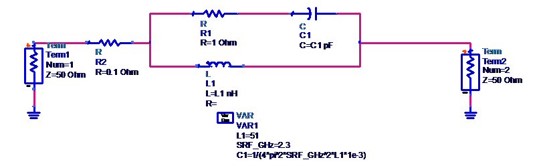

둘째, 인덕터를 살펴보고, 인덕터 성능에 중요한 부품들과 사양은 무엇인지 살펴볼 것입니다.

셋째, 저항에 대해 알아보고, 어떻게 고주파수에서 동작하는지를 살펴볼 것입니다.

넷째, 트랜스포머와 PLL(Phase Locked Loop)을 살펴보고, PLL 내부 회로를 검토하여 민감한 부분과 우선순위를 부여하지 않아도 되는 부분을 확인해 보도록 할 것입니다.

그런 다음 오실레이터를 살펴보겠습니다. 전압 제어 오실레이터를 중심으로, 튜닝 전압, 전원공급 레귤레이터 및 필요한 경우 차폐와 관련한 모범사례를 살펴보도록 하겠습니다.

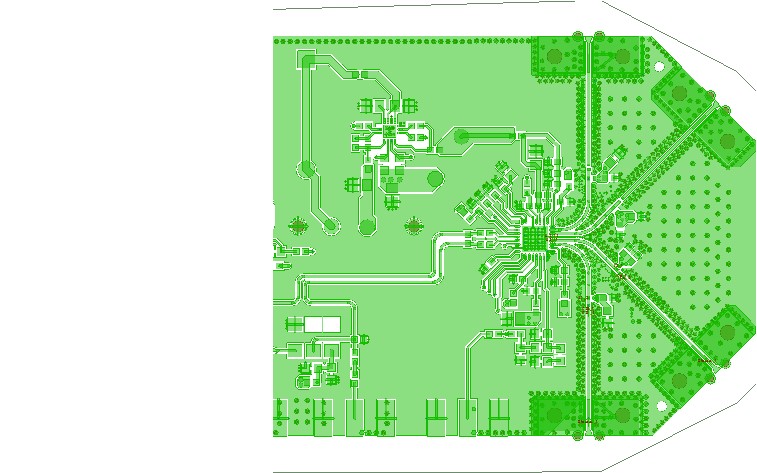

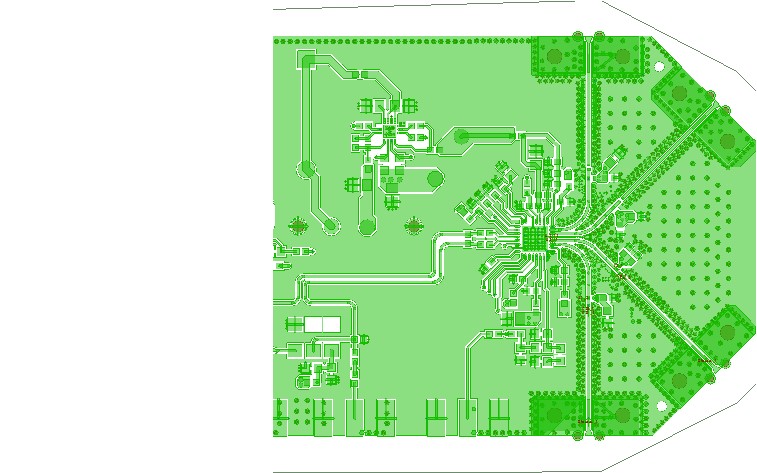

마지막으로는 직접 ADF4356을 사용한 작업 예제를 보여드릴 것입니다.

RF 및 microwave, 고속 mixed signal 분야의 통신장비 또는 계측장비 분야에서 활동하시는 설계자분들의 많은 참여를 부탁 드립니다.

웨비나 주요내용

-LPF(Low-Pass Filter)와 RF 회로와 커패시터

-인덕터 성능과 사양

-저항 및 동작 형태

-트랜스포머와 PLL(Phase Locked Loop)

-오실레이터 사용 모범 사례

최상의 PLL의 성능을 유지하고, spurious emission 및 주변 소자간 interference를 최소화하는 기법에 대해 설명할 것입니다.

본 웨비나의 발표자 이안 콜린스는 아나로그 디바이스사의 Microwave Frequency generation group의 application manager로서, PLL 및 VCO제품에 대한 전문가입니다.

웨비나에서 다뤄볼 내용은 다음과 같습니다.

첫째, 이러한 유형의 PCB의 특성상 전송 라인 이론과 사용 가능한 다른 유전체 재료를 검토하는 것이 중요하기 때문에, 수동 부품 선택 및 관련한 모범 사례를 살펴보고, LPF(Low-Pass Filter)와 RF 회로에 적합한 커패시터에 대해 알아볼 것입니다.

둘째, 인덕터를 살펴보고, 인덕터 성능에 중요한 부품들과 사양은 무엇인지 살펴볼 것입니다.

셋째, 저항에 대해 알아보고, 어떻게 고주파수에서 동작하는지를 살펴볼 것입니다.

넷째, 트랜스포머와 PLL(Phase Locked Loop)을 살펴보고, PLL 내부 회로를 검토하여 민감한 부분과 우선순위를 부여하지 않아도 되는 부분을 확인해 보도록 할 것입니다.

그런 다음 오실레이터를 살펴보겠습니다. 전압 제어 오실레이터를 중심으로, 튜닝 전압, 전원공급 레귤레이터 및 필요한 경우 차폐와 관련한 모범사례를 살펴보도록 하겠습니다.

마지막으로는 직접 ADF4356을 사용한 작업 예제를 보여드릴 것입니다.

RF 및 microwave, 고속 mixed signal 분야의 통신장비 또는 계측장비 분야에서 활동하시는 설계자분들의 많은 참여를 부탁 드립니다.

웨비나 주요내용

-LPF(Low-Pass Filter)와 RF 회로와 커패시터

-인덕터 성능과 사양

-저항 및 동작 형태

-트랜스포머와 PLL(Phase Locked Loop)

-오실레이터 사용 모범 사례

아나로그 디바이스 어플리케이션 엔지니어

Ian Collins

웨비나 댓글

- 52 Comments

- 노*래 (2021-03-18 오전 11:32:40)

- 등록합니다

- 이*진 (2019-04-24 오후 1:42:01)

- 수고하셨습니다.

- 장*식 (2019-04-16 오후 4:42:31)

- 5번, 6변 배선은 배선 중간에 line width가 달라지는데 이렇게 되어도 impedance에 영향이 없을까요? 비 연속성이 발생하여 impedance 비 매칭이 되는것이 아닐지, 그리고 보통 FR4 사용 하고 GHz 대역의 고속신호라면 line width 도 매우 좁을것으로 (50옴 기준) 예상되는데 해당 라인 배선시 직각 부분에 0.7만큼 깍아내는게 tool로 가능할지 현실적으로 구현은 어려워 보입니다.

- 장*식 (2019-04-16 오후 4:40:05)

- 6페이지 고속 라인 배선사례에서 6가지 예(좌측 위부터 1번, 2번, 3번)가 제안되었는데 보통 일선에서는 3번, 4번을 많이 사용하고 있습니다.

- 장*식 (2019-04-16 오후 4:18:29)

- 222페이지 VCO를 레퍼런스로 나눈값이 60이하여야 한다. 는 공식에 대한 상세 자료나 레퍼런스 문서등이 제안될수 있을까요? 해당 내용을 이해 못했습니다.

- 장*식 (2019-04-16 오후 3:28:23)

- 강의 감사합니다. 강의 발표자료는 내려받기가 안되나요?

- 김*열 (2019-04-16 오전 10:33:32)

- 출석합니다.

- 홍*화 (2019-04-16 오전 10:32:25)

- 감사합니다.

- 박*훈 (2019-04-16 오전 10:31:01)

- 세미나 출첵이요ㅋ

- H*W (2019-04-16 오전 10:28:12)

- 업무 관련한 유익한 내용이 될 것 같습니다.